射频集成电路是连接数字世界与无线物理世界的桥梁,广泛应用于智能手机、物联网、卫星通信等领域。其设计融合了模拟电路、数字电路与高频电磁场理论,复杂度极高,工程师在设计过程中常面临一系列挑战。本文将系统性地探讨射频集成电路设计中的几个核心难题,并提供相应的解决思路与方案。

一、 常见问题分析

- 噪声与线性度之间的权衡: 这是射频设计永恒的矛盾。低噪声放大器需要工作在低偏置电流以最小化噪声,但这会牺牲线性度,导致处理大信号时产生失真。反之,提高线性度往往引入更多噪声。

- 阻抗匹配与带宽限制: 射频信号对阻抗极其敏感。实现50欧姆的宽带阻抗匹配非常困难,尤其是在片上集成的电感、电容参数受工艺偏差影响较大的情况下。窄带匹配容易实现,但限制了电路的应用范围。

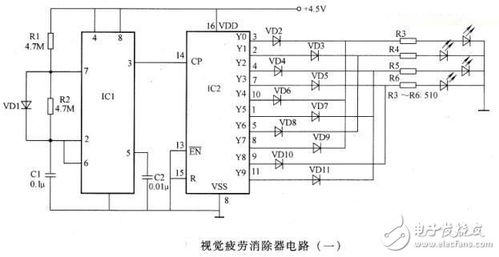

- 寄生效应与隔离度: 在高频下,导线电感、衬底耦合、封装寄生等效应变得不可忽视。电源线与信号线之间的耦合、不同电路模块之间的串扰(如本振泄漏到射频端口),会严重恶化系统性能,如接收机灵敏度、发射机频谱纯度等。

- 工艺波动与模型不准: 先进半导体工艺的器件尺寸不断缩小,工艺波动对射频性能(如截止频率、噪声系数)的影响加剧。高频下的器件模型(特别是无源器件如电感、变压器)往往不够精确,导致仿真与实测结果存在差距。

- 功耗与性能的平衡: 移动设备对功耗有严苛要求。如何在满足增益、线性度、噪声等指标的前提下,尽可能降低功耗,是设计中的一大挑战。

二、 核心解决方案与设计策略

针对上述问题,现代射频IC设计发展出多种应对策略:

- 架构级优化:

- 噪声与线性度: 采用电流复用、噪声消除、导数叠加等技术。例如,在低噪声放大器中使用并联反馈或共源共栅结构,可以在一定范围内改善线性度而不显著增加噪声。对于混频器等模块,可采用无源混频器或电流导引结构来获得更好的线性度。

- 系统规划: 合理分配系统级联中各模块的增益、噪声和线性度指标,避免某个模块成为性能瓶颈。利用先进的数字校准和预失真技术来补偿模拟电路的线性度不足。

- 电路与版图协同设计:

- 阻抗匹配: 使用片上自动调谐网络、可编程电容阵列等自适应匹配技术来应对工艺偏差和频率变化。采用多级匹配或宽带匹配拓扑(如分布式放大器)来拓展带宽。

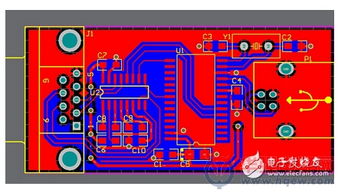

- 隔离与抗寄生: 在版图上,大量使用保护环、深N阱隔离、接地屏蔽层来减少衬底耦合。对敏感线路采用差分走线。电源线必须精心设计去耦网络,使用高质量(高Q值)的片上电容和封装上的分立电容组合。将数字与射频模块物理隔离,并采用独立的电源域和接地。

- 模型与工艺的深度结合:

- 设计前期: 与晶圆代工厂紧密合作,获取更精确的射频工艺设计套件,特别是针对无源元件的电磁仿真模型。

- 设计后期: 必须进行全芯片的电磁联合仿真,以评估大信号下的耦合效应。采用蒙特卡洛分析来评估工艺角变化对性能的影响,并在设计中预留足够的裕量或可调单元。

- 低功耗设计技术:

- 采用亚阈值或弱反型区设计技术,在极低电压电流下工作。

- 设计高性能的电源管理单元,为射频电路提供多路可调、低噪声的电源。

- 利用电路休眠、功率分级等系统策略,根据通信需求动态调整射频前端的功耗。

三、 未来趋势与

随着5G/6G、毫米波通信和硅基工艺的持续演进,射频集成电路设计正朝着更高频段、更宽带宽、更高集成度和更智能化方向发展。面临的挑战将更加严峻,但解决方案也在不断革新。例如,利用人工智能辅助进行电路优化和版图生成,采用异构集成(如将GaAs、SiGe与CMOS集成)来获得最佳性能,以及通过系统级封装技术来整合最优的射频单元。

总而言之,成功的射频集成电路设计没有单一的“银弹”,它要求工程师深刻理解高频物理、电路原理、半导体工艺和系统应用,并在复杂的多目标约束中做出精巧的权衡与创新。通过架构创新、精心设计与先进工具的紧密结合,才能攻克难题,打造出高性能、高可靠的射频芯片。